### ASSEMBLY AND INTERCONNECTION TECHNOLOGIES

### FOR WBG POWER SEMICONDUCTOR

### POWER ELECTRONICS

MARTIN RITTNER, ROBERT BOSCH GMBH

'TECHNOLOGIES FOR ENERGY SUSTAINABILITY'

UNIVERSITY OF PADUA SUMMER SCHOOL IN INFORMATION ENGINEERING

IN CONJUNCTION WITH H2020 PUBLIC FUNDED RESEARCH PROJECT INREL-NPOWER

BRESSANONE/BRIXEN, JULY 5<sup>TH</sup> 2017

Universita

DEGLI STUDI

DI PADOVA

DI INGEORERA

DELLINFORMAZIONE

- ► Introduction and system definitions

- ► Assembly and interconnection technologies

- Materials' basics

- Specific technologies: Ag-Sintering, diffusion soldering, Cu-bonding

- ► Components to join

- Power semiconductor

- Substrates and circuit carriers

- Examples of modern wide-band-gap power module concepts

- ► Reliability assessment

- Principle aspects: Loads on power electronics and examples of failure mechanisms

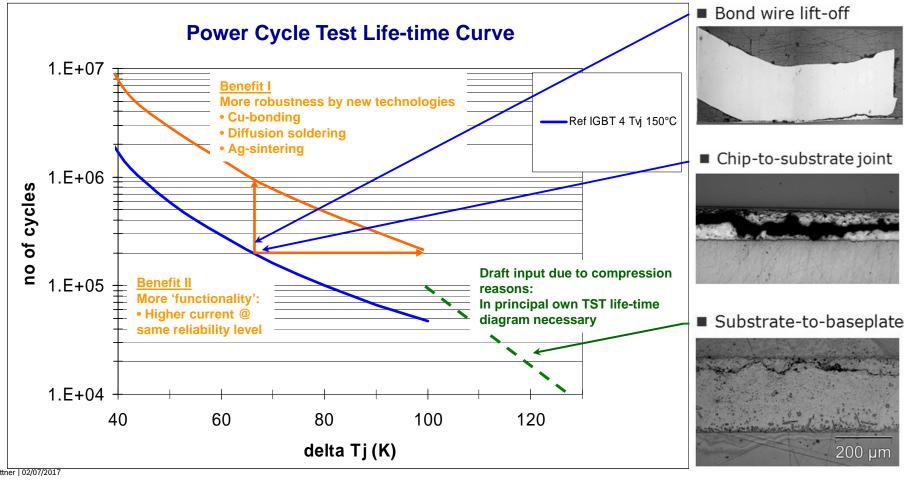

- Power cycle test premises and life-time curves

- 'Robustness Validation' methodology

- ► Summary

- ► Introduction and system definitions

- ► Assembly and interconnection technologies

- Materials' basics

- Specific technologies: Ag-Sintering, diffusion soldering, Cu-bonding

- ► Components to join

- Power semiconductor

- Substrates and circuit carriers

- ► Examples of modern wide-band-gap power module concepts

- ► Reliability assessment

- Principle aspects: Loads on power electronics and examples of failure mechanisms

- Power cycle test premises and life-time curves

- 'Robustness Validation' methodology

- Summary

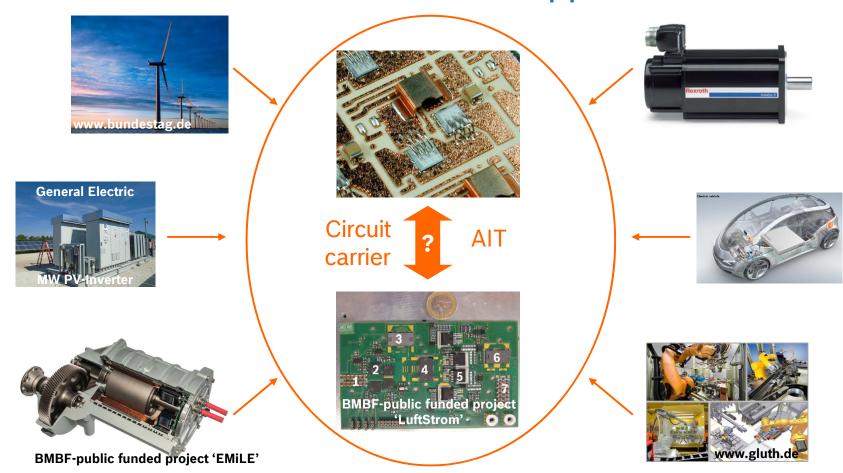

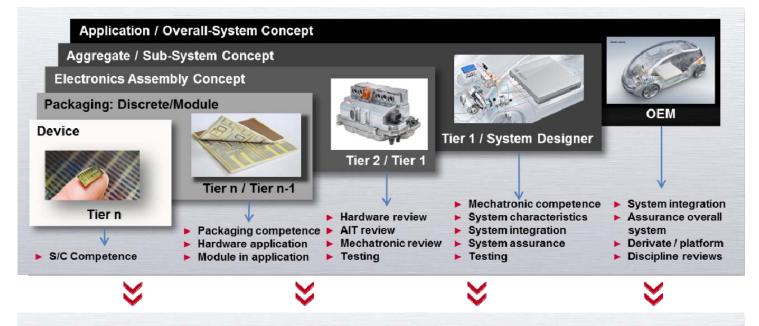

## Modern High Performance AIT for WBG PSC PE System Definition I: Power Electronics Application

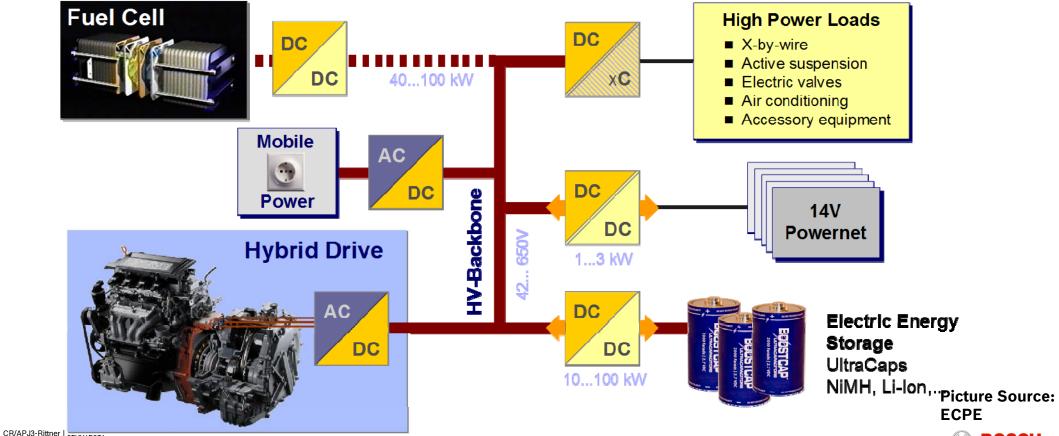

## System Definition II: Automotive Electrified Powertrain System

### Power Electronic Key Systems for the Cars of Tomorrow

InRel

Università degli Studi

DI PADOVA

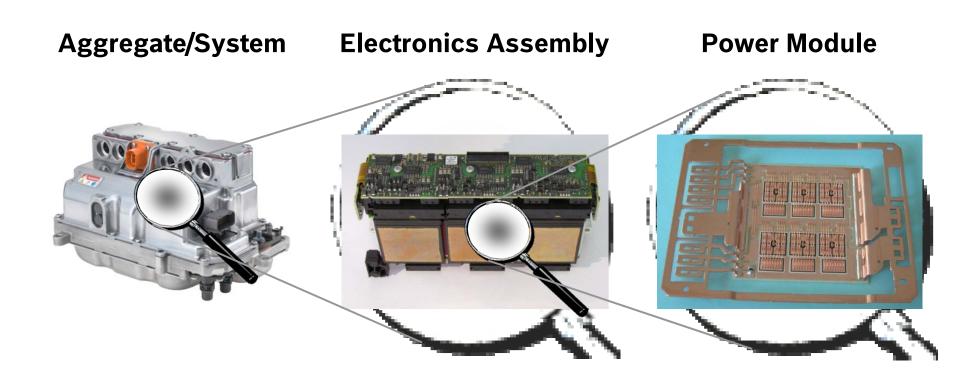

# Modern High Performance AIT for WBG PSC PE System Definition III: Built-up Levels (Example Drive Inverter)

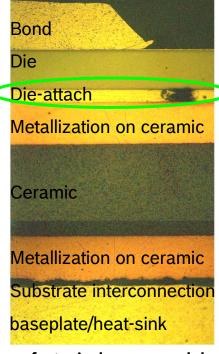

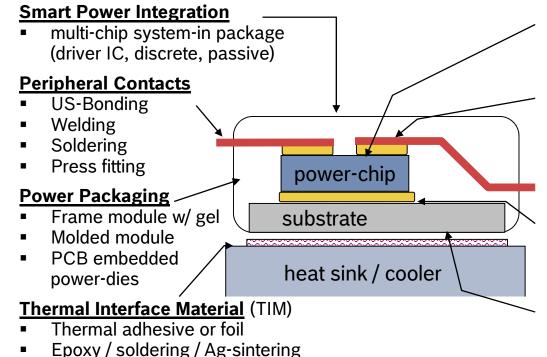

## Modern High Performance AIT for WBG PSC PE System Definition IV: Level of Electronics Packaging

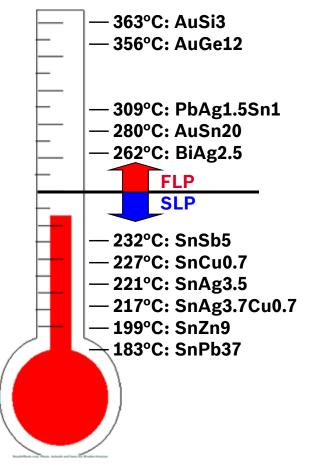

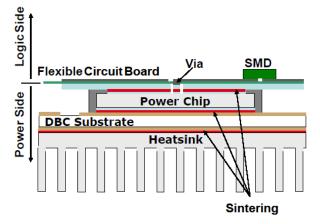

### First Level Packaging (FLP)

- ▶ Bare-dies on a substrate w/ 'housing'

- Discrete's packaging

- Power module

- ► AITs of bare die

- ▶ Die-attach

- ▶ Bonding

- **...**

Cross section of a typical power module

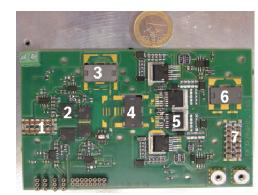

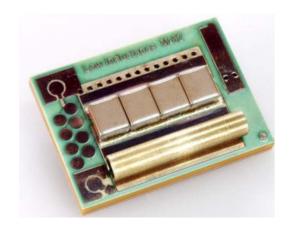

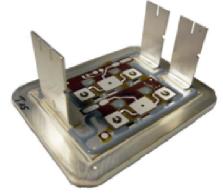

### **Second Level Packaging (SLP)**

- ► Complex mixture of components on a substrate

- Discrete actives

- Diverse passives

- Diverse sensors

- Plugs and connectors

- **...**

- ► AITs on pcb

- SMD reflow soldering

- SMD adhesives

- THD selective soldering

- THD press fitting

- THD screwing

SLP of a DC/DC-converter BMBF-public funded project 'LuftStrom'

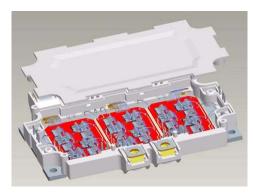

## Modern High Performance AIT for WBG PSC PE System Definition Va: Power Module Technologies

### Module base technologies

▶ Open construction module

**Picture Source:** M. Thoben. Infineon. within BMBF Public funded project 'ProPower'

▶ Molded module

**Picture Source:** F. Osterwald, Danfoss, within BMBF **Public funded** project 'ProPower'

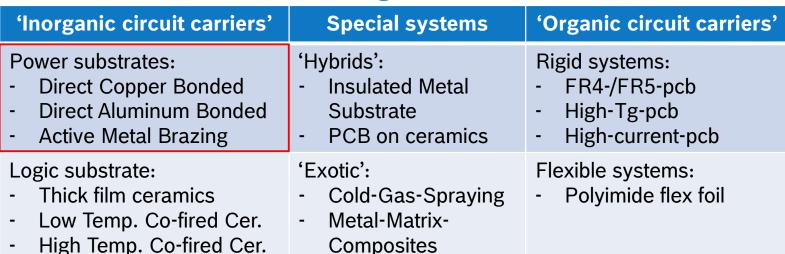

### **Diversified module technologies**

- ► Circuit carrier

- Ceramics (DCB, AMB)

- Lead-frame, ...

- ► Die-attach power semiconductor

- Solder

- Ag-sintering, diffusion-soldering

- ► Top-side contact Chip

- Al-bonding

- Cu-bonding

- ► Semiconductor metallization

- AlSiCu, Ni/Au, Cu, ...

- ► Chip-mounting und therm. management

- Single-sided joining and contacting

- Double-sided joining

- ► Module-mounting on cooler

- Polymeric thermal interface material

- Soldering

- Ag-sintering

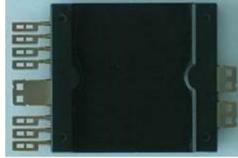

## System Definition Vb: Power Module AIT Design Elements

#### **Power Semiconductors**

- S

- SiC, GaN

- Chip-metallization

#### **Top-Electrode**

- Al-bond material

- Cu-bond material

- Cu-clip soldered

- Cu-clip Ag-sintered

#### **Die-Attach**

- Soldering

- Diffusion soldering

- Ag-sintering, sinter adhesive

#### **Circuit carrier**

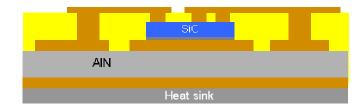

- DCB, DAB, AMB: Al<sub>2</sub>O<sub>3</sub>, Si<sub>3</sub>N<sub>4</sub> or AlN ceramics

- Cu-lead frame / Insulated Metal Substrate

- ► Introduction and system definitions

- Assembly and interconnection technologies

- Materials' basics

- Specific technologies: Ag-Sintering, diffusion soldering, Cu-bonding

- ► Components to join

- Power semiconductor

- Substrates and circuit carriers

- ► Examples of modern wide-band-gap power module concepts

- ► Reliability assessment

- Principle aspects: Loads on power electronics and examples of failure mechanisms

- Power cycle test premises and life-time curves

- 'Robustness Validation' methodology

- Summary

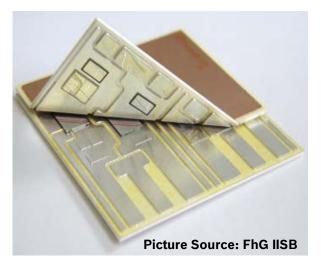

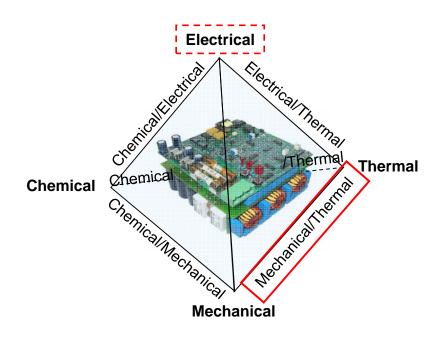

# Modern High Performance AIT for WBG PSC PE Functions of Assembly and Interconnection Technologies

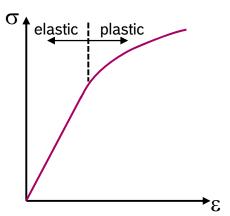

#### ▶ Mechanical

- Young's modulus E

- Shear modulus G

- Plastic deformation

- Stress-strain-characteristics σ−ε

- Bending strength

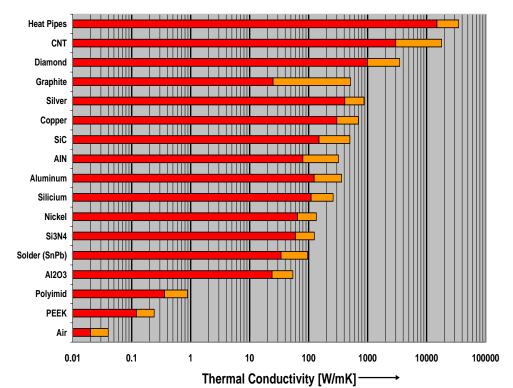

#### **▶** Thermal

- Coefficient of thermal expansion  $\alpha$

- Specific conductivity λ<sub>th</sub>

- Absolute resistance R<sub>th</sub> bzw. Z<sub>th</sub>

#### **▶** Electrical

- Specific conductivity  $\lambda_{el}$

- Absolute resistance R<sub>Ohm</sub>

Picture Source: Prof. Martin März, FhG IISB

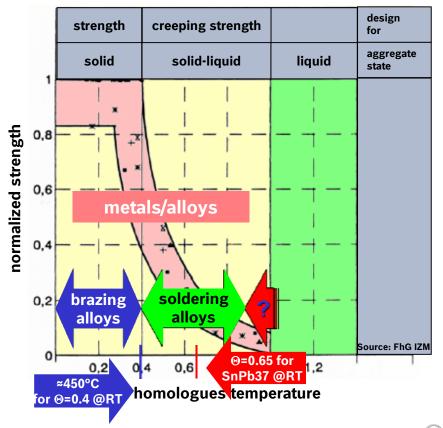

# Modern High Performance AIT for WBG PSC PE (Solder) Material Characteristics

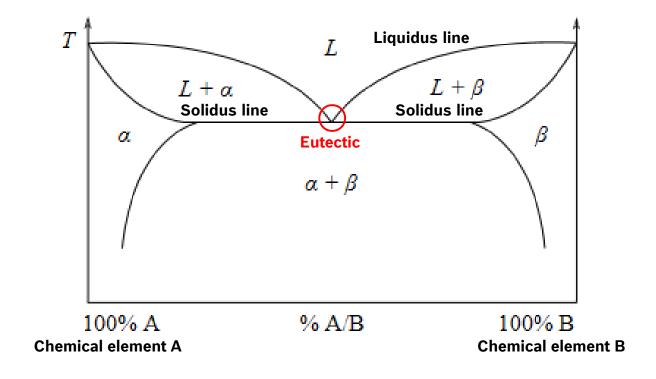

- ► Metallurgical alloy: (non-)eutectic binary (e.g. SnPb, BiAg, AuSn, ...), ternary (e.g. SnAgCu), ... (e.g. 'InnoLot-alloy' SnAgCuSbBiNi), further 'dopants' (e.g. precipitation hardening, ....)

- ▶ Microstructure: morphology (e. g. grains), diffusion (e. g. intermetallic compound IMC), grain coarsening, sliding of grain boundaries, ...

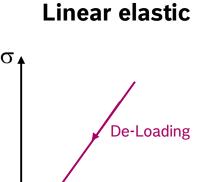

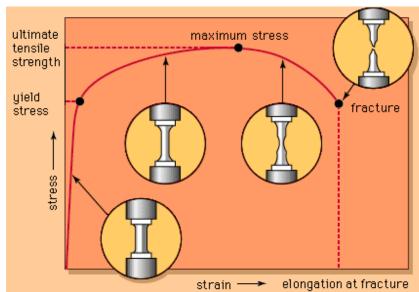

- ▶ Physical Properties: Young's modulus, stress-strain-properties (e.g. elastic, plastic, visco-plastic, creep, ...)

- ► **Fatigue:** crack initiation and crack progress, physics-of-failure, statistical distributions, ...

**Never forget: (Solder) Material systems are quit complex systems**

# UNIVERSITA DEGLI STUDI DI PADOVA DIPATIMENTO DI INGEGNERA DELLINFORMAZIONE

## Basics on Stress-Strain-Relationships

### **Tensile sample tester**

Picture source: www.zwick.de

σ = E x ε'Hook's Law'

oading

### **Plasticity**

Picture source: www.totalmaterial.com

# Modern High Performance AIT for WBG PSC PE Binary Phase Diagram Liquid-Solid

InRel

Università degli Studi

DI PADOVA

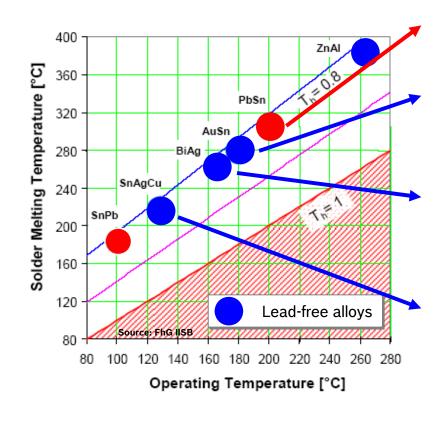

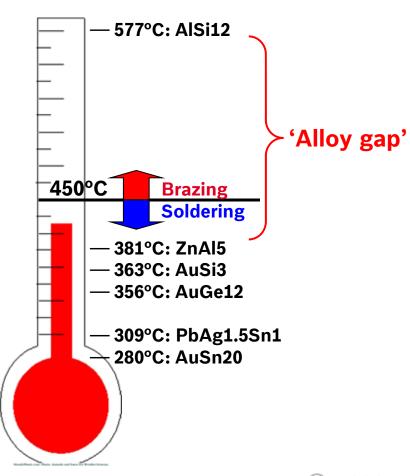

# Modern High Performance AIT for WBG PSC PE High Melting Solder Alloys

- ▶ Pb95Sn5

- High ductility

- Process and reliability reference

- ► Au80Sn20

- High cost alternative

- Little brittleness

- Excellent wetting

- ▶ Bi97.5Ag2.5

- Low cost alternative

- High brittleness

- Bi same chemical group as Pb

- ► Sn96.5Ag3.0Cu0.5

- Preferred substitute for Sn63Pb37

- Robust processes

- Reliable alloy up to 125°C

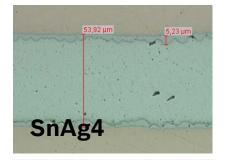

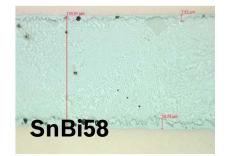

# Modern High Performance AIT for WBG PSC PE Solders at their limit?

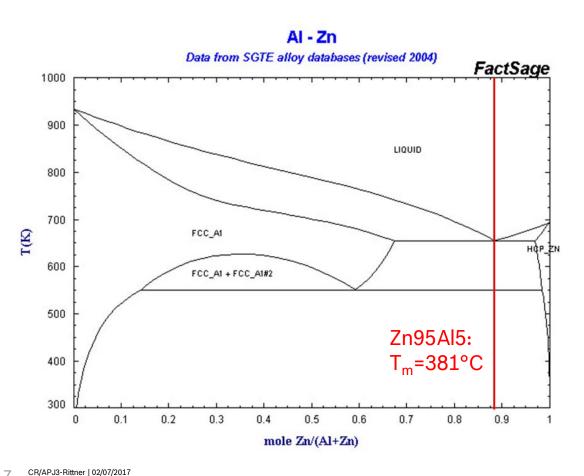

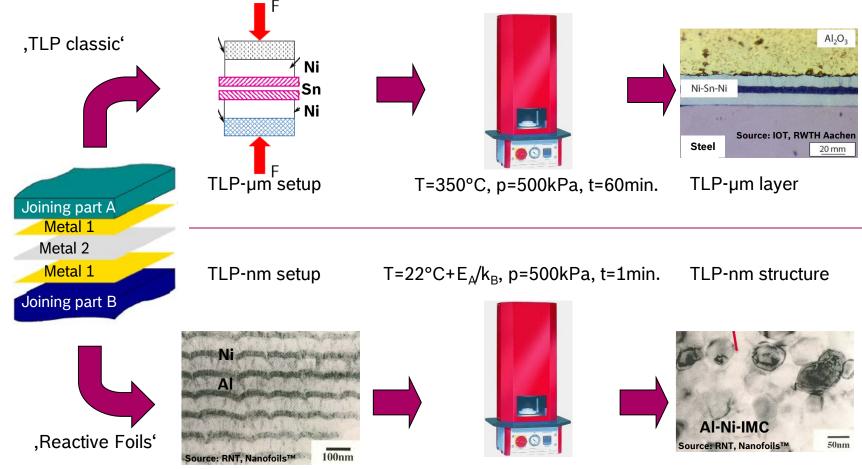

Transient Liquid Phase Diffusion Soldering (1)

# Modern High Performance AIT for WBG PSC PE Transient Liquid Phase Diffusion Soldering (2)

- ► High melting metals:

- Au, Ag, Cu, Ni, ...

- ► Low melting metals:

- Sn, Ge, In, ...

- ► Established die-attach systems

- Au-Sn or (Si-)Au-Sn with few µm of Au as dieattach (e. g for opto-electronic devices)

- ► High temperature capability due to primary IMC microstructure

- Open technology questions

- Reliability in power cycle tests?

- Cost-level for power semiconductors?

#### **Reactive Foils:**

- ► Commercially available:

- e.g. RNT Nanofoils™

- ► Interfacial characteristics:

- soldered-like

- brazed-like

- ▶ Due to sputter processes for the nm-scale: costly

- ► But further research activities ongoing, especially to raise layers on (sub)µm-scale thicknesses w/o losses in processability

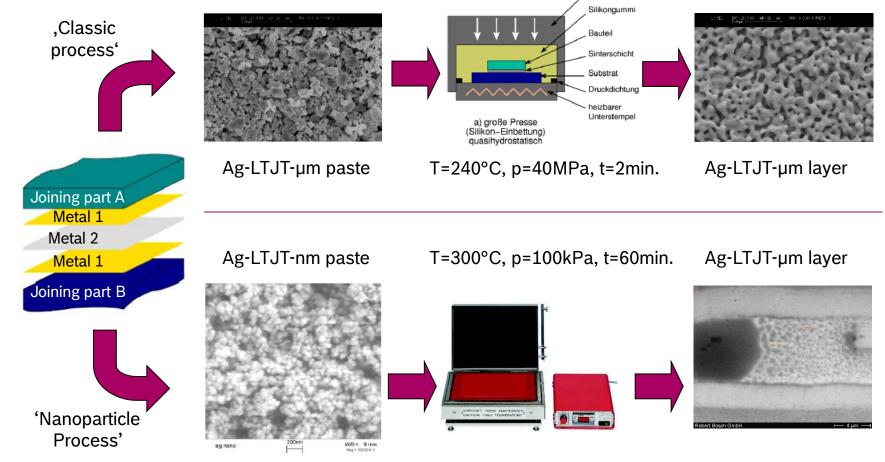

Low Temperature Joining Technology (LTJT, Ag-Sintering) (1)

### LTJT classic process:

- Pastes are commercially available

- ► Functionalizes surfaces of joining partners

- Ag, Ni/Au (e.g. ENIG), Cu-blank (under development)

- ► Characteristics of joint

- Dense, low porous joint with good connection to joined partner surfaces ⇒ maximal reliability

- ► Industrialized for single-sided power modules

- Open technology questions

- Process transfer to double-sided systems?

- Integration of further components in power module while applying just one process step?

### LTJT nanoparticle process:

- ► Pastes are commercially available

- ► Functionalizes surfaces of joining partners

- Ag, Ni/Au (e.g. ENIG), Cu-blank (under development)

- ► Characteristics of joint

- Porous joint with reduced connection to joined partner surfaces ⇒ reduced reliability

- ► Industrialized for LED-applications

- ► Open technology questions

- Process transfer to molded power modules w/o losses in reliability?

- Easier integration ability of further components?

## Modern High Performance AIT for WBG PSC PE **US-Bonding Technology on Power Semiconductors**

### **Standard Aluminium US-Bonding**

- ▶ Well established process on PSC

- Heavy wire

- Ribbon bond

- ► Chip metallization AlSi, AlCu, AlSiCu (~3 µm) is typically designed for this process landscape

- Limitations

- Electrical conductivity

- Thermal conductivity

- Power cycle Robustness

Al-ribbon bonds on Si-MOSFET

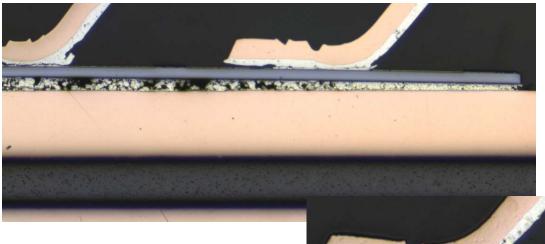

### **New Copper US-Bonding**

- ► Processes under development

- Heavy wire

- Ribbon bond

- ▶ New chip metallization is needed

- Damage in active S/C-structure w/ standard metallization under bond

- Change to thicker Cu-metallization (≃40 µm)

- Wafer-bowing

- ► Improvements

- ► Electrical conductivity

- ▶ Thermal conductivity

- Power cycle robustness

**Cu-bonds on PSCs**

- ► Introduction and system definitions

- ► Assembly and interconnection technologies

- Materials' basics

- Specific technologies: Ag-Sintering, diffusion soldering, Cu-bonding

- ► Components to join

- Power semiconductor

- Substrates and circuit carriers

- ► Examples of modern wide-band-gap power module concepts

- ► Reliability assessment

- Principle aspects: Loads on power electronics and examples of failure mechanisms

- Power cycle test premises and life-time curves

- 'Robustness Validation' methodology

- Summary

# Modern High Performance AIT for WBG PSC PE Power Semiconductor: General Requirements

| Technological requirement                             | Typical state of the art values Si IGBT                                                  | Foreseeable values SiC MOSFET                                                                                                                 | Foreseeable values GaN HEMT                                 |

|-------------------------------------------------------|------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|

| Maximum operating chip temperature                    | T <sub>junction,max.</sub> = 150°C (175°C)                                               | 175°C ≤ T <sub>junction,max.</sub> ≤ 250°C                                                                                                    | 175°C ≤ T <sub>junction,max.</sub> ≤ 250°C                  |

| Current density                                       | 2 A/mm <sup>2</sup>                                                                      | 3 A/mm²                                                                                                                                       | ≥3 A/mm²                                                    |

| $\Delta T$ with at least 10 <sup>6</sup> power cycles | 60 K                                                                                     | 100 K                                                                                                                                         | 100 K                                                       |

| Power dissipation density                             | 0,4 W/cm <sup>3</sup>                                                                    | 0,6 W/cm <sup>3</sup>                                                                                                                         | ≥ 0,6 W/cm³                                                 |

| Module R <sub>th,j-c</sub>                            | ≃ 1 K/W                                                                                  | ≃ 0,1 K/W                                                                                                                                     | ≃ 0,1 K/W                                                   |

| Switching Frequencies and<br>Switching Gradients      | 9 kHz ≤ f <sub>sw</sub> ≤ 11<br>dl/dt ≃ 10 kA/μs ⇒ 15 nH ≤ L <sub>stray</sub> *) ≤ 20 nH | 24 kHz $\leq$ f <sub>sw</sub> $\leq$ 48 kHz (hard switching)<br>dl/dt $\simeq$ 20 kA/ $\mu$ s $\Rightarrow$ L <sub>stray</sub> *) $\leq$ 6 nH | 24 kHz ≤ f <sub>sw</sub> ≤ 1 MHz<br>(hard → soft switching) |

| Integration of passives in module                     | Not assigned                                                                             | Capacitors<br>Resistors                                                                                                                       | Capacitors<br>Resistors                                     |

| Integration of actives in module                      | Not assigned                                                                             | Gate-driver or<br>μ-controller                                                                                                                | Gate-driver or µ-controller (already on chip-design-level)  |

<sup>\*)</sup> including peripheral module contacts

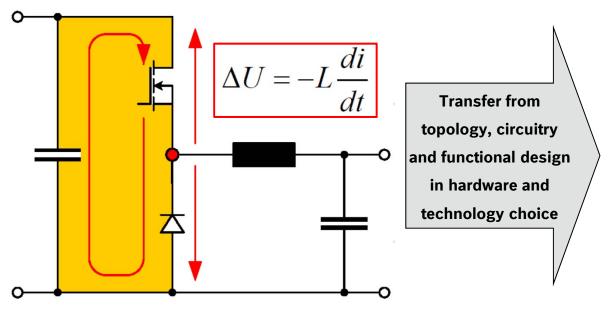

# Power Semiconductor: Fast Switching and Parasitic Inductance

Picture Source: Ch. Göbl, SemiKron

# Integration capability (increase in functionality and added value)

Logic-power-integration (especially w/ respect of active components, ...)

Integration of passive components (e.g. C, I-Sensor, T-Sensor, ...)

Increased integration depth of thermal management

Mechatronic integration (aggregate level)

InRel

Universită degli Studi

DI PADOVA

DI INGEGNERIA DELL'INFORMAZIONI

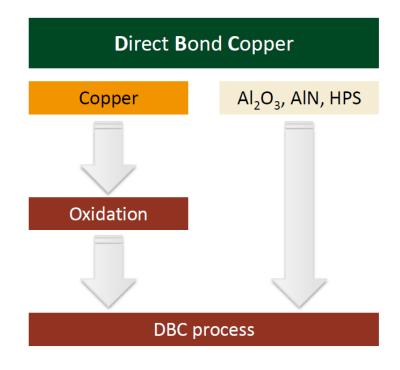

## Modern High Performance AIT for WBG PSC PE DCB- and AMB-Substrates I: Process Technologies

- Process temperature approx. 1065° C

- Eutectic melt reaction between ceramic and copper

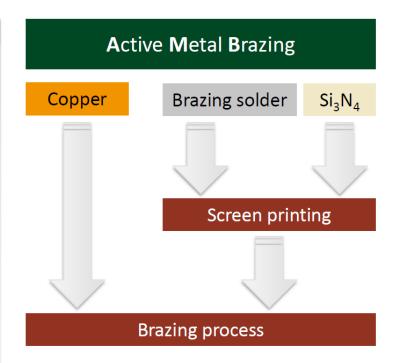

- Process temperature approx. 800° C

- High temperature brazed joint between ceramic and copper

Picture Source: K. Schmidt, Rogers Corp.

# Modern High Performance AIT for WBG PSC PE DCB- and AMB-Substrates II: Characteristics

|                                                          | curamik® Power                                   | curamik®<br>Power Plus                            | curamik®<br>Thermal | curamik®<br>Performance        |  |

|----------------------------------------------------------|--------------------------------------------------|---------------------------------------------------|---------------------|--------------------------------|--|

| * Values are for bare ceramics ** curamik internal tests |                                                  |                                                   |                     |                                |  |

| © Ceramic Type                                           | Al <sub>2</sub> O <sub>3</sub>                   | HPS<br>(Zr doped Al <sub>2</sub> O <sub>3</sub> ) | AIN                 | Si <sub>3</sub> N <sub>4</sub> |  |

| Thermal Conductivity [W/mK]@20°C *                       | 24                                               | 26                                                | 170                 | 90                             |  |

| CTE [ppm/K] 20-300°C *                                   | 6.8                                              | 7.1                                               | 4.7                 | 2.5                            |  |

| Bending Strength<br>[N/mm²] *                            | 450                                              | 600                                               | 350                 | 700                            |  |

| Fracture Toughness [MPa/ $\sqrt{m}$ ] *                  | 4.2                                              | 5.0                                               | 3.4                 | 6.0                            |  |

| Peeling strength **                                      | ≥ 4 N/mm                                         |                                                   |                     | ≥ 10 N/mm                      |  |

| Dielectric Strength (DC)<br>[kV/mm] *                    | 20                                               |                                                   |                     |                                |  |

| Master Card size                                         | 138 mm x 190.5 mm (usable area: 127 mm x 178 mm) |                                                   |                     |                                |  |

Picture Source: K. Schmidt, Rogers Corp.

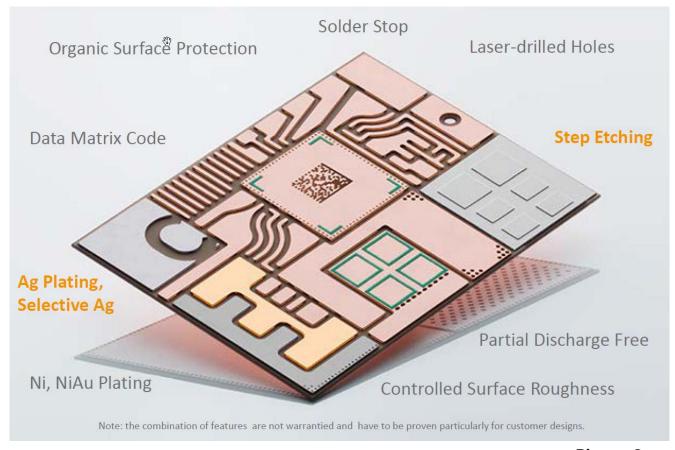

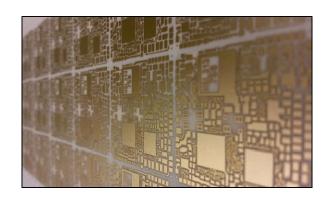

### Modern High Performance AIT for WBG PSC PE DCB- and AMB-Substrates III: Customization

Picture Source: K. Schmidt, Rogers Corp.

- ► Introduction and system definitions

- ► Assembly and interconnection technologies

- Materials' basics

- Specific technologies: Ag-Sintering, diffusion soldering, Cu-bonding

- ► Components to join

- Power semiconductor

- Substrates and circuit carriers

- ► Examples of modern wide-band-gap power module concepts

- ► Reliability assessment

- Principle aspects: Loads on power electronics and examples of failure mechanisms

- Power cycle test premises and life-time curves

- 'Robustness Validation' methodology

- Summary

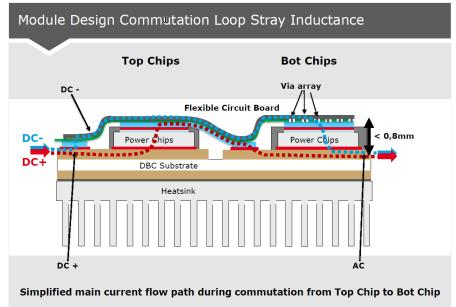

- ► Half-bridge-module, single phase

- ▶ Power class 5 kW

- ▶ 'Extreme' design optimization of commutation cell to a level of lowest possible parasitic inductance

- ► DBC-substrate with a high voltage blocking SiC-JFET laminated in one prepreg layer

- ► DC-link-inductance: 0,6 nH

- ► Technology selection on 'academic level'

Picture Source: Prof. Eckart Hoene, FhG IZM

## Low-inductance fast switching SiC-module w/ lowest EMI (2)

InRel

- ► Half-bridge-module, single phase

- ▶ Power class 400 kW

- ► Good design optimization of commutation cell to a very low level of parasitic inductance

- ▶ DBC-substrate with a high voltage blocking SiC-MOSFET laminated in flex-foil-substrate

- ▶DC-link-inductance: ~1 nH

- ► Technology close to industrialization

Picture Source: Ch. Göbl, SemiKron

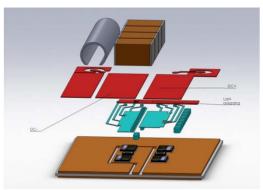

## InRel-Npower: Low-inductance fast switching GaN-module

- ► Full-bridge-module, three phase

- ► Power class 20 kW 30 kW

- ► Under research investigation in the InRel-NPower project:

- Si3N4-AMB-substrate with a high voltage blocking GaN-HEMT and with a second 'counter substrate' as a LTCC multilayer ceramics

- Boundaries of design optimization of commutation cell?

- Reachable DC-link-inductance down to 1 nH?

- Technology boundaries on the way to the industrialization of this hardware design concept?

Università degli Stud

- ► Introduction and system definitions

- Assembly and interconnection technologies

- Materials' basics

- Specific technologies: Ag-Sintering, diffusion soldering, Cu-bonding

- ► Components to join

- Power semiconductor

- Substrates and circuit carriers

- ► Examples of modern wide-band-gap power module concepts

- ► Reliability assessment

- Principle aspects: Loads on power electronics and examples of failure mechanisms

- Power cycle test premises and life-time curves

- 'Robustness Validation' methodology

- Summary

InRel

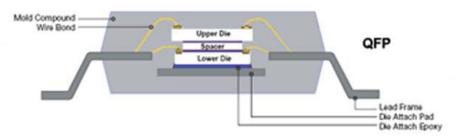

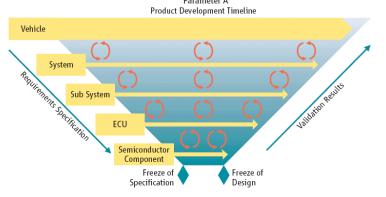

#### Functionality and Robustness Validation on Electronics Design upon all chain links

- ▶ Design starts already upon device (design, testing, screening / usage in application / life-time)

- OEM competence mission down to Tier n

- Discussion about application and mission profile with S/C-manufacturer / hardware assembler

- Expert's dialog along supply chain (Tier n... Tier 1)

- Competence development at Tier n ... Tier 1

**Picture Source:** B. Hellenthal, Audi AG. within the BMBF public funded project 'ProPower'

DI PADOVA DI INGEGNERIA DELL'INFORMAZIONE

UNIVERSITÀ DEGLI STUDI InRel

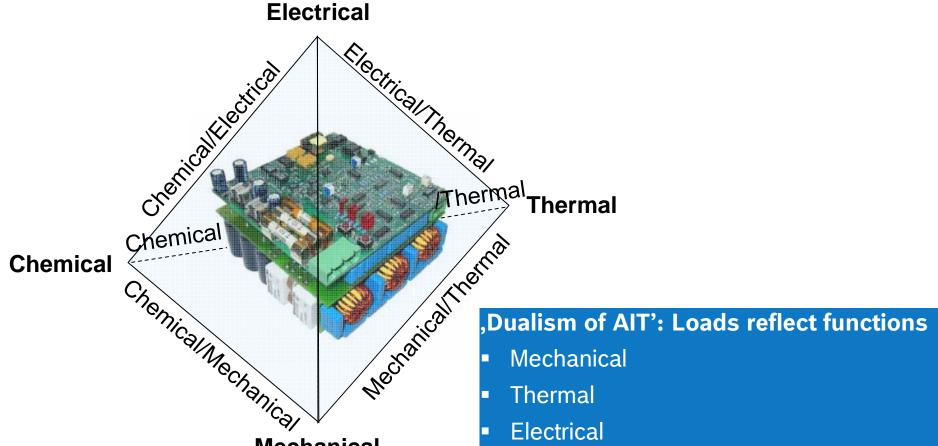

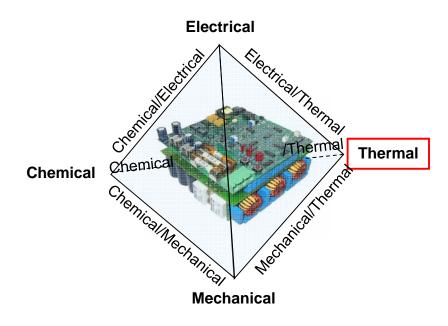

Spectra of Loads

**Electrical**

**Mechanical**

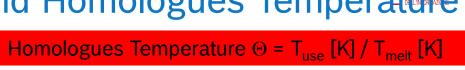

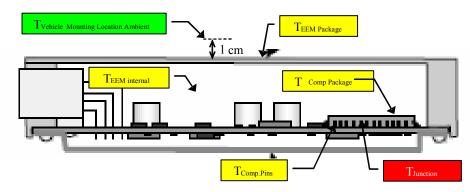

## Loads on Power Electronics: Temperature

- ► Definitions of temperatures must be clear

- junction, component, substrate, ambient, ...

- ► Consideration of temperature over time

- ► Maximum Operating Temperatures?

- Depends on chosen technology base and components

- Circuit carrier, especially pcb

- Discrete mold package

- **-** ...

## Modern High Performance AIT for WBG PSC PE Loads on Power Electronics: Temperature Cycles

### **Passive Cycle Testing (ambient condition)** (Temperature Cycle Test, TCT)

- ► Embossment by ambient: homogenous through heating and cooling

- ▶ shock condition in a two chamber funeral system

- ramped condition in a single chamber funeral system

- ► -40°C/+125°C, -40°C/+150°C swings are typically

- ► 30'/30' minutes dwell time is typically

### **Power Cycle Testing (active condition) (PCT)**

- ► Embossment by current: temperature gradients

- ► Short-term period (≈1s) for near-chip bond-technology

- ► Long-term period (≈30s) for near chip die-attachtechnology

### **PCT-result in a soldered die-attach system:**

Bond contacts and die-attach show typically a mixed failure mode

#### **PCT-Result in a Ag-sintered die-attach system:**

Typically just bond contacts show failure mode

But for pure Cu-bonding this effect is not valid any longer

# UNIVERSITA DEGLI STUDI DI PADOVA DI INGEGNERA DELINFORMAZIONE

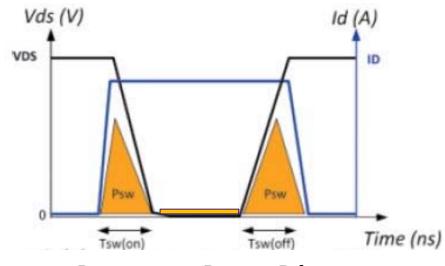

### **Hard switching:**

- Voltage and current change at same time

- DC-AC-drive invertertype w/ f<sub>sw</sub> ≈ 20 kHz

- ► Each switching event 'counts down life-time'

- ► Immediate PCTscenario

$$P_{losses\ total} = Ps_{tat} + Pd_{yn}$$

$$P_{losses\ total} = \int V_{ds}(t) \times I_d(t) dt$$

$$P_{losses\ total} = [V_{ds} \times Id]_{steady\ state} + \int_{sw\ on} V_{ds}(t) \times I_{d}(t)dt + \int_{sw\ off} V_{ds}(t) \times I_{d}(t)dt$$

### Soft switching (ZVS):

- Voltage and current change phase shifted

- DC-DC-converter-type w/ f<sub>sw</sub> ≥ 100 kHz up to 1 MHz

- Switching events average to elevated mid-term temperature level

- More similarity to TCTscenario

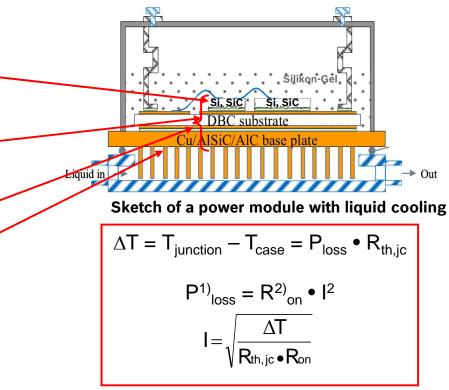

# **Power Cycle Test Premises**

### **Premises of Power Cycle Test**

- ► Power semiconductor defines maximum T<sub>iunction</sub>

- Semiconductor, AIT und circuitry causes power losses P<sub>loss</sub>

- ► Module design and AIT-materials' stack generate therm. resistance R<sub>th.ic</sub>

- ► Thermal management defines T<sub>case</sub>

- ► Temperature swings ∆T causes thermomechanical stress at different CTEs between devices and substrate

- 1) Disregarding dynamic losses

- 2) Semiconductor and peripherals

### Università DEGLI STUDI DI PADOVA

InRel

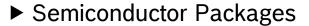

# Modern High Performance AIT for WBG PSC PE Semiconductor & AEC-Q100/-Q101

- Discrete for logic/ASIC

- Discrete for power

- Bare-die

- Typical for power modules

- ▶ Qualification referred to AEC-Q100/-Q101

- Determined by descriptions of stress tests

- Pre-defined stress tests with pre-defined load conditions

- Sample lot sizes typical 45 ... 77 pieces within 1 ... 3 lots

- Passed/not passed criteria

- Objective in its origin: approval of samples for customer provision

- Utilization meanwhile as 'product and field-approval qualification'

- Maximum applying remains yet on the level of 'fit for test'

Typical design mold package for discrete device

### **Robustness Validation**

InRel

#### ▶ Semiconductor

- Removal of lack in AEC-Q100/-Q101

- Change towards 'fit for application'

- Design for reliability/robustness

- Description of the Mission Profile as core column

- Derivation and performing of valid loading- and life-time tests

- 'Knowledge based qualification'

#### ► ECUs

- Systematic expansion of RV-methodology on the ECU level

- Mission Profile (incl. manufact,/assembly)

- Failure mechanisms and failure modes

- Accelerating models for failure mechanisms

- Field relevant accelerated testing

Picture Sources: Robustness Validation Handbooks, ZVEI

# Modern High Performance AIT for WBG PSC PE Wide-Band-Gap Power Modules

# UNIVERSITA DEGLI STUDI DI PADOVA DIPARTIMENTO DI INSEGNERIA DELI INSEGNERIA

- ► Intensified trend towards SiC-MOSFET-basing power modules, in industrial applications and as well in automotive drive inverters, is foreseeable

- Data points in technology life-time curve, that reflect highly accelerated conditions at high ∆T (≥ 100 K) for current Si-IGBT-based modules, will be data points for typical field loads in future SiC-MOSFET-basing modules

- ► SiC-MOSFET-performance higher switching frequencies and steeper switching gradients leads to distinct higher module complexity in design and chosen AIT

- Low-inductive 'planar-design'

- ► Spatial close mounting of DC-link capacitor and integrated passive/active components

- ⇒ Effects on testability plus failure mechanisms/modes and root-cause analysis after loading are probably

Low-inductive SiC-MOSFET basing Power Module Picture Source: E. Hoene, FhG IZM, CIPS-conference 2014

Low-inductive SiC-MOSFET basing Power Module Picture Source: P. Beckedahl, SemiKron, CIPS-conference 2016

- ► Introduction and system definitions

- ► Assembly and interconnection technologies

- Materials' basics

- Specific technologies: Ag-Sintering, diffusion soldering, Cu-bonding

- ► Components to join

- Power semiconductor chip

- Substrates and circuit carriers

- ► Examples of modern wide-band-gap power module concepts

- ► Reliability assessment

- Principle aspects: Loads on power electronics and examples of failure mechanisms

- Power cycle test premises and life-time curves

- 'Robustness Validation' methodology

### ► Summary

- ► Power electronics assembly and interconnection technology is a complex 'cross-disciplinary science' between the science disciplines materials' science, physics, chemistry, electronics engineering, mechanical engineering, ...

- ► Modern high performance AIT for WBG power semiconductor power electronics considers

- Low-inductive power electronics design for fast switching and steep voltage and current gradients

- New technology variations or even completely new technologies 'beyond state of the art'

- High temperature capability due to higher in application usable T<sub>iunctions</sub>

- Thermal cycle robustness in TCT and PCT

- Qualification routines: general ones and new upcoming specific ones

- ▶ WBG power semiconductors are 'precious' devices: AIT has to support their outperformance

Never forget: each power electronics design has to be 'physical incarnated' as hardware

- ⇒ Assembly and interconnection technology has to be mastered

- ⇒ Wide-band-gap power electronics demands new design boundaries